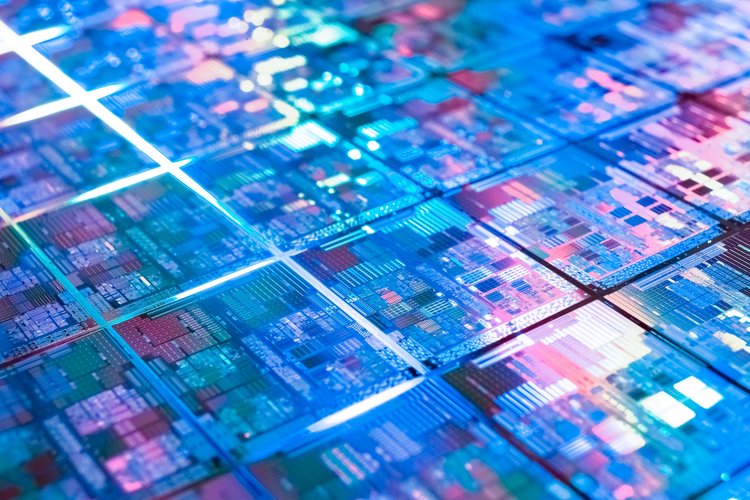

A team of researchers at the Massachusetts Institute of Technology (MIT) has successfully developed a new superconducting memory array that significantly reduces error rates, a critical advancement for the future of quantum computing. Published on January 25, 2026, in the journal Nature Electronics, this innovative memory system utilizes superconducting nanowires, aiming to enhance the efficiency and reliability of quantum computers.

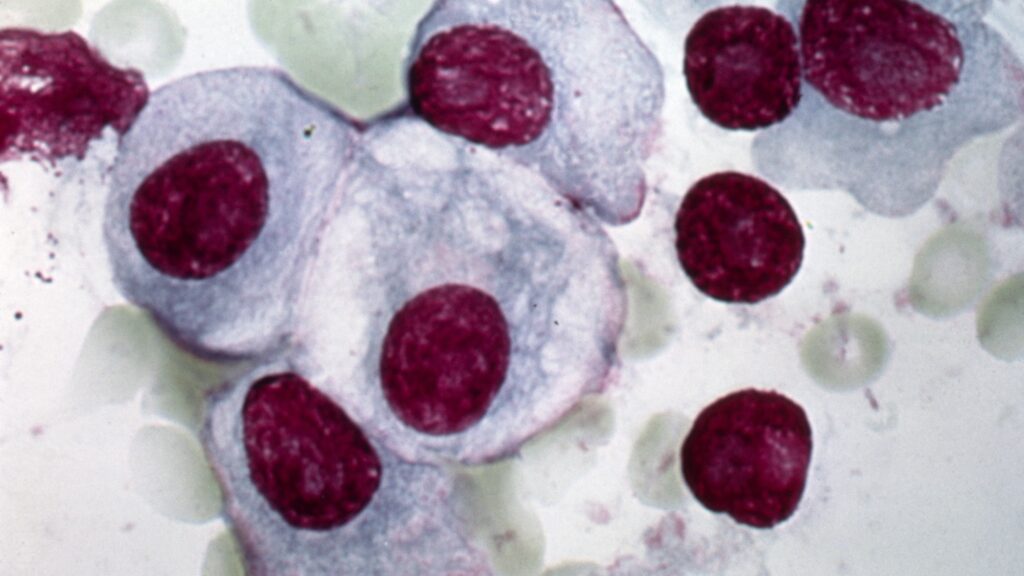

Superconducting memory devices are known for their potential to operate with zero electrical resistance when cooled below a specific temperature. This property makes them ideal for high-speed and low-energy consumption tasks in computing. However, conventional superconducting memories have limitations, particularly in terms of scalability and error rates. The new array developed at MIT addresses these issues by introducing a scalable design that minimizes errors during operation.

The researchers’ superconducting memory array is built around compact 4 × 4 configurations of nanowires, each comprising a superconducting loop with two temperature-dependent switches and a variable kinetic inductor. This design allows for efficient row-column operations, achieving a functional density of 2.6 Mbit cm −2.

Owen Medeiros, Matteo Castellani, and their colleagues outlined the importance of this advancement in their paper, stating, “Scalable superconducting memory is required for the development of low-energy superconducting computers and fault-tolerant quantum computers.” They noted that traditional superconducting memory cells occupy a larger footprint, which limits their scalability. In contrast, the new nanowire-based cells are more compact, yet previous designs had suffered from high error rates.

The team conducted extensive tests on their nanowire memory array, achieving an impressive error rate of approximately 1 in 100,000 operations, equating to a minimum bit error rate of 10 −5. This performance indicates a significant improvement over previous superconducting memory technologies, making this array one of the most reliable to date.

The operation of the memory cells is intricate yet efficient. Each cell writes and reads data through precisely timed electrical pulses, which temporarily heat one of the nanowire switches. This process increases the switch’s resistance and allows for the injection of magnetic flux into the loop, effectively encoding data values of zero or one. Once the pulse ends, the nanowire returns to its superconducting state, trapping the information securely.

This recent development is poised to advance the field of superconducting memory, potentially facilitating its deployment in practical applications. With further refinement, the researchers believe their design could lead to the creation of larger, more reliable memory systems that could support the growing demands of quantum computing.

As the quest for faster and more efficient computing continues, the work by MIT’s research team marks a significant step towards the realization of scalable superconducting memory architectures. With ongoing advancements, the future of memory technologies appears increasingly promising.